다른 명령

편집 요약 없음 |

편집 요약 없음 |

||

| 5번째 줄: | 5번째 줄: | ||

CXL는 3개의 프로토콜로 나뉠 수 있다. | CXL는 3개의 프로토콜로 나뉠 수 있다. | ||

[[파일:CXL Usages.png|프레임없음|가운데|700픽셀]] | |||

; CXL.io | ; CXL.io | ||

: PCIe의 IO와 같은 규격을 가진다. | : PCIe의 IO와 같은 규격을 가진다. | ||

| 11번째 줄: | 11번째 줄: | ||

: CPU Host에서 디바이스로의 Direct접근을 말한다. | : CPU Host에서 디바이스로의 Direct접근을 말한다. | ||

; CXL.cache | ; CXL.cache | ||

: Device에서 CPU로 캐쉬 Coherent한 Direct Access가 가능하게 하는 프로토콜이다. | : Device에서 CPU로 캐쉬 Coherent한 Direct Access가 가능하게 하는 프로토콜이다. | ||

== CXL Cache/Memory Hierarchy == | |||

[[파일:CXL Cache memory hierarchy.png|700px|프레임없음|가운데]] | |||

:CXL.mem 프로토콜은 메모리 디바이스에 DDR처럼 연결되어 캐싱 환경을 제공한다. CPU가 보기에, DDR과 CXL.mem 프로토콜을 동일한 기능을 제공한다. | |||

:CXL.cache 프로토콜은 디바이스 캐쉬 (upto 1MB in CXL 1.1)과의 Consistency를 제공한다. | |||

CPU Cache와 CXL캐쉬는 [[MESI]]프로토콜을 사용하여서 서로 cache state를 공유한다. MESI는 각각의 캐쉬라인 주소를 얻는데 사용된다. | |||

2023년 2월 3일 (금) 07:18 판

개요

Compute Express Link(CXL)은 PCIe에 장착하는 새로운 프로토콜로 캐쉬와 메모리에 최적화된 구조를 가지고 있다. CXL은 auto-negotiate란 특성을 사용해서 PCIe에 NVMe와 같은 PCIe용 프로토콜이 사용되면 그 모드로 아니면 CXL모드로 자동 전환되는 구조를 가지고 있다.

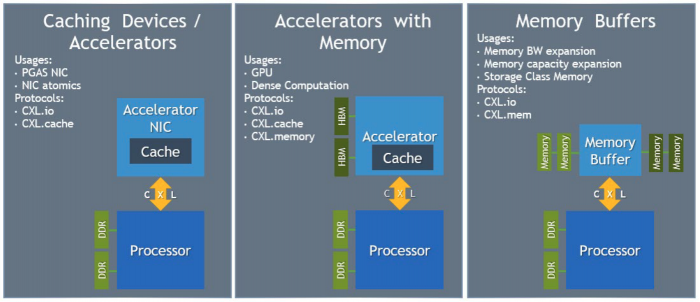

CXL는 3개의 프로토콜로 나뉠 수 있다.

- CXL.io

- PCIe의 IO와 같은 규격을 가진다.

- CXL.memory(CXL.mem)

- CPU Host에서 디바이스로의 Direct접근을 말한다.

- CXL.cache

- Device에서 CPU로 캐쉬 Coherent한 Direct Access가 가능하게 하는 프로토콜이다.

CXL Cache/Memory Hierarchy

- CXL.mem 프로토콜은 메모리 디바이스에 DDR처럼 연결되어 캐싱 환경을 제공한다. CPU가 보기에, DDR과 CXL.mem 프로토콜을 동일한 기능을 제공한다.

- CXL.cache 프로토콜은 디바이스 캐쉬 (upto 1MB in CXL 1.1)과의 Consistency를 제공한다.

CPU Cache와 CXL캐쉬는 MESI프로토콜을 사용하여서 서로 cache state를 공유한다. MESI는 각각의 캐쉬라인 주소를 얻는데 사용된다.