다른 명령

새 문서: 분류: 메모리 인터페이스 == 개요 == Compute Express Link(CXL)은 PCIe에 장착하는 새로운 프로토콜로 캐쉬와 메모리에 최적화된 구조를 가지고 있다. CXL은 auto-negotiate란 특성을 사용해서 PCIe에 NVMe와 같은 PCIe용 프로토콜이 사용되면 그 모드로 아니면 CXL모드로 자동 전환되는 구조를 가지고 있다. CXL는 3개의 프로토콜로 나뉠 수 있다. ; CXL.io : PCIe의 IO와 같은... |

편집 요약 없음 |

||

| (같은 사용자의 중간 판 2개는 보이지 않습니다) | |||

| 1번째 줄: | 1번째 줄: | ||

[[분류: | [[분류: 컴퓨터 인터페이스]] | ||

== 개요 == | == 개요 == | ||

| 5번째 줄: | 5번째 줄: | ||

CXL는 3개의 프로토콜로 나뉠 수 있다. | CXL는 3개의 프로토콜로 나뉠 수 있다. | ||

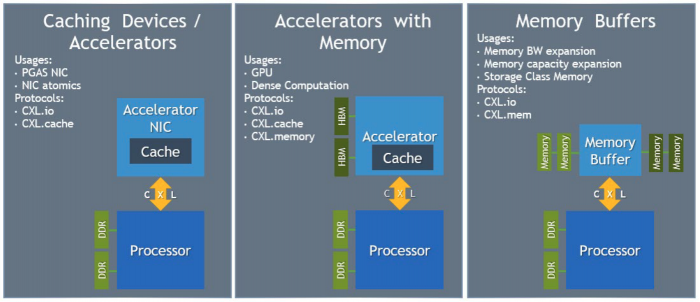

[[파일:CXL Usages.png|프레임없음|가운데|700픽셀]] | |||

; CXL.io | ; CXL.io | ||

: PCIe의 IO와 같은 규격을 가진다. | : PCIe의 IO와 같은 규격을 가진다. | ||

| 11번째 줄: | 11번째 줄: | ||

: CPU Host에서 디바이스로의 Direct접근을 말한다. | : CPU Host에서 디바이스로의 Direct접근을 말한다. | ||

; CXL.cache | ; CXL.cache | ||

: Device에서 CPU로 캐쉬 Coherent한 Direct Access가 가능하게 하는 프로토콜이다. | : Device에서 CPU로 캐쉬 Coherent한 Direct Access가 가능하게 하는 프로토콜이다. | ||

== CXL Cache/Memory Hierarchy == | |||

[[파일:CXL Cache memory hierarchy.png|700px|프레임없음|가운데]] | |||

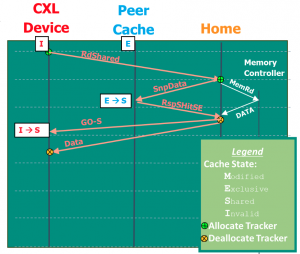

* CXL은 Asymmetric cache coherency protocol MESI를 통해서 관리된다. | |||

* CXL.mem 프로토콜은 메모리 디바이스에 DDR처럼 연결되어 캐싱 환경을 제공한다. CPU가 보기에, DDR과 CXL.mem 프로토콜을 동일한 기능을 제공한다. | |||

* CXL.cache 프로토콜은 디바이스 캐쉬 (upto 1MB in CXL 1.1)과의 Consistency를 제공한다. | |||

* CPU Cache와 CXL캐쉬는 [[MESI]]프로토콜을 사용하여서 서로 cache state를 공유한다. MESI는 각각의 캐쉬라인 주소를 얻는데 사용된다. CXL디바이스 사이의 캐쉬 상태는 Host가 주도적으로 관리하며 CXL device transparent하게 cache state 공유를 제공한다. | |||

=== CXL Snoop === | |||

[[파일:CXL Read Flow.png|프레임없음|오른쪽]] | |||

CXL Host (CPU)는 CXL 디바이스, 현재 코어 그리고 다른 [[NUMA]] Core처럼 여러 하드웨어의 CXL Cache의 Consistency를 맞추어 주어야 한다. 이를 위해서 Device는 Request나 Snoop과 같은 간단한 명령어를 통해서 이 작업을 수행한다. | |||

== Reference == | |||

# https://www.electronicdesign.com/technologies/embedded-revolution/article/21162617/cxl-coherency-memory-and-io-semantics-on-pcie-infrastructure | |||

# https://www.snia.org/educational-library/cxl-11-protocol-extensions-review-cache-and-memory-protocols-cxl-2020 | |||

2023년 2월 3일 (금) 09:57 기준 최신판

개요

Compute Express Link(CXL)은 PCIe에 장착하는 새로운 프로토콜로 캐쉬와 메모리에 최적화된 구조를 가지고 있다. CXL은 auto-negotiate란 특성을 사용해서 PCIe에 NVMe와 같은 PCIe용 프로토콜이 사용되면 그 모드로 아니면 CXL모드로 자동 전환되는 구조를 가지고 있다.

CXL는 3개의 프로토콜로 나뉠 수 있다.

- CXL.io

- PCIe의 IO와 같은 규격을 가진다.

- CXL.memory(CXL.mem)

- CPU Host에서 디바이스로의 Direct접근을 말한다.

- CXL.cache

- Device에서 CPU로 캐쉬 Coherent한 Direct Access가 가능하게 하는 프로토콜이다.

CXL Cache/Memory Hierarchy

- CXL은 Asymmetric cache coherency protocol MESI를 통해서 관리된다.

- CXL.mem 프로토콜은 메모리 디바이스에 DDR처럼 연결되어 캐싱 환경을 제공한다. CPU가 보기에, DDR과 CXL.mem 프로토콜을 동일한 기능을 제공한다.

- CXL.cache 프로토콜은 디바이스 캐쉬 (upto 1MB in CXL 1.1)과의 Consistency를 제공한다.

- CPU Cache와 CXL캐쉬는 MESI프로토콜을 사용하여서 서로 cache state를 공유한다. MESI는 각각의 캐쉬라인 주소를 얻는데 사용된다. CXL디바이스 사이의 캐쉬 상태는 Host가 주도적으로 관리하며 CXL device transparent하게 cache state 공유를 제공한다.

CXL Snoop

CXL Host (CPU)는 CXL 디바이스, 현재 코어 그리고 다른 NUMA Core처럼 여러 하드웨어의 CXL Cache의 Consistency를 맞추어 주어야 한다. 이를 위해서 Device는 Request나 Snoop과 같은 간단한 명령어를 통해서 이 작업을 수행한다.