다른 명령

편집 요약 없음 |

편집 요약 없음 |

||

| (같은 사용자의 중간 판 2개는 보이지 않습니다) | |||

| 1번째 줄: | 1번째 줄: | ||

[[분류: CPU]] | [[분류: CPU]] | ||

[[분류: 디바이스]] | [[분류: 디바이스]] | ||

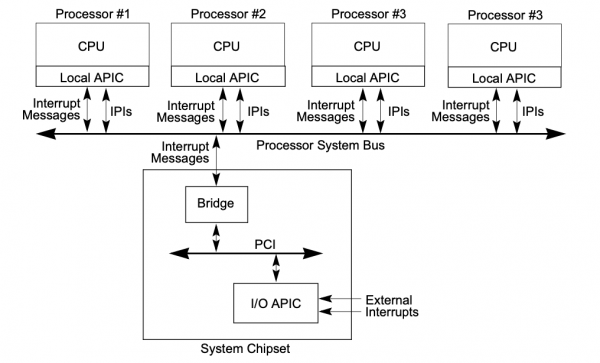

[[파일:APIC Overview.png|600px|프레임없음|가운데]] | |||

== 개요 == | == 개요 == | ||

APIC은 Interrupt Controller중의 하나로, 기존의 [[PIC]]보다 훨씬 발전된 방식의 Interrupt 처리 루틴이다. APIC은 Local LAPIC과 IOAPIC으로 분리되어 구현되어 있다. LAPIC은 각각의 | APIC은 Interrupt Controller중의 하나로, 기존의 [[PIC]]보다 훨씬 발전된 방식의 Interrupt 처리 루틴이다. 원래는 8235 PIC칩이 인터럽트를 수행하였는데, 속도와 기능상의 이유로 Interrupt처리 루틴을 개선하여 CPU에 집어넣었다. APIC은 Local LAPIC과 IOAPIC으로 분리되어 구현되어 있다. LAPIC은 각각의 프로세서 안에 박혀있으며, IOAPIC은 시스템의 버스에 박혀있다. APIC의 목적은 프로세서의 인터럽트를 처리하여 지정된 코어에 전달하는 것과, Multicore환경에서 [[IPI]]를 주고 받는 것이다. | ||

== LAPIC == | == LAPIC == | ||

LAPIC은 각각의 코어마다 하나씩 할당되어 있다. 이 LAPCI은 서로 인터럽트를 발생시켜서 [[IPI]]을 발생시킬 수도 있으며, 최대 0~31개의 인터럽트 처리와 32~225개의 지정된 인터럽트 처리를 할 수 있다. | LAPIC은 각각의 코어마다 하나씩 할당되어 있다. 이 LAPCI은 서로 인터럽트를 발생시켜서 [[IPI]]을 발생시킬 수도 있으며, 최대 0~31개의 인터럽트 처리와 32~225개의 지정된 인터럽트 처리를 할 수 있다. Local APIC과 같은 경우에는 프로세서의 코어에 직접 연결되어 있는 I/O 장치, APIC Timer, IPI, Performance monitoring counter, Thermal Sensor와 같은 코어의 직접연관된 인터럽트를 수행하는 역활을 한다. LAPIC은 HPET를 지원한다. [[HPET]]란 높은 정밀도의 타이머로써, 각각의 코어들이 하나의 타이머에 대해서 경쟁하지 않아도 현재 타임에 대한 정확한 값을 가져올 수 있도록 도와준다. 만약 APIC이 활성화되어 HPET가 지원되면 8253pic은 사용되지 않도록 비활성화 된다. | ||

각각의 인터럽트들이 어떻게 행동할지에 대한 정의는 Local vector table (LVT)라는 것을 통해서 설정할 수 있다. LVT는 APIC, xAPIC과 같은 경우에는 [[MMIO]]를 통해서 메모리 접근으로 컨트롤 하였으며, [[x2APIC]]과 같은 경우에는 [[MSR]]레지스터를 통해서 컨트롤 한다. Local Vector Table은 어떤 하드웨어 인터럽트를 코어의 인터럽트 핀으로 전달할지를 결정한다. | |||

== | == I/OAPCI == | ||

I | I/O APIC과 같은 경우는 외부 장비의 인터럽트를 적절한 코어에 전달하는 것이다. I/O APIC을 통해서 전달된 인터럽트는 LVT를 참고하여서 Local APIC으로 전달되어 최종적으로 코어에 전달된다. I/O APIC과 같은 경우에는 시스템 버스에 연결된 하드웨어나 I/O Device로부터 생성된 인터럽트를 코어에 전달하는 것이다. | ||

I/O APCI은 Redirection table을 가지고 있다. 이는 각각의 장치에서 들어온 인터럽트를 지정된 인터럽트 번호로 매핑시킨다. 기존의 8253인터럽트 침과 같은 경우는 오직 16개의 외부 인터럽트만을 지원하였는데, APIC은 redirection을 통해서 하드웨어에 할당된 0x20이전의 인터럽트를 제외한 최대 224개의 인터럽트를 추가로 지원할 수 있다. | |||

== APIC Timer == | |||

APIC은 3개의 타이머 모드를 허용한다. | |||

; Periodic Mode | |||

: Periodic Mode에서는 소프트웨어가 (Typically, 운영체제가 된다.) 특정한 기간을 설정하여서 APIC에게 주기적인 Timer interrupt을 발생 시켜 달라고 요청하는 모드이다. 예를 들어서 Perioidic 모드에서는 소프트웨어는 APIC에 1ms마다 주기적으로 타이머 인터럽트를 넣어달라고 요청하게 된다. | |||

; One-shot Mode | |||

: Periodic Mode와 비슷하지만, 단 한번만 일어나도록 요청을 내리는 모드이다. 소프트웨어는 APIC에거 얼마간 뒤에 타이머 인터럽트를 발생 시켜 달라고 요청하게 된다. 예를 들어서 소프트웨어는 APIC에게 1ms뒤에 타이머 인터럽트를 넣어달라고 요청하게 된다. | |||

; TSC-Deadline Mode | |||

: TSC Deadline Mode는 다른 두개의 타이머 모드와는 약간 이질적인 특성이 있다. 특정 Timer interval을 전송하는 것이 아니라, [[TSC]]라는 코어의 Time stamp counter의 값이 특정 값 이상이 되면 타이머 인터럽트를 넣어달라고 요청하는 방법이다. 이 방식은 다른 두개의 방식보다 더욱 정확한 TSC라는 Timer을 사용하고 (다른 방식들은 CPU Frequency를 사용한다), Race condition을 피하기 쉬운 특징이 있다. 예를 들어서 소프트웨어는 APIC에게 현재 TSC Count가 100000 일경우 100000 + <math>\alpha</math>인 100050이 되면 타이머 인터럽트를 발생시켜 달라고 요청하게 된다. | |||

== References == | |||

# Intel 64 and Ia-32 Software Developer's Manual | |||

2023년 4월 21일 (금) 05:26 기준 최신판

개요

APIC은 Interrupt Controller중의 하나로, 기존의 PIC보다 훨씬 발전된 방식의 Interrupt 처리 루틴이다. 원래는 8235 PIC칩이 인터럽트를 수행하였는데, 속도와 기능상의 이유로 Interrupt처리 루틴을 개선하여 CPU에 집어넣었다. APIC은 Local LAPIC과 IOAPIC으로 분리되어 구현되어 있다. LAPIC은 각각의 프로세서 안에 박혀있으며, IOAPIC은 시스템의 버스에 박혀있다. APIC의 목적은 프로세서의 인터럽트를 처리하여 지정된 코어에 전달하는 것과, Multicore환경에서 IPI를 주고 받는 것이다.

LAPIC

LAPIC은 각각의 코어마다 하나씩 할당되어 있다. 이 LAPCI은 서로 인터럽트를 발생시켜서 IPI을 발생시킬 수도 있으며, 최대 0~31개의 인터럽트 처리와 32~225개의 지정된 인터럽트 처리를 할 수 있다. Local APIC과 같은 경우에는 프로세서의 코어에 직접 연결되어 있는 I/O 장치, APIC Timer, IPI, Performance monitoring counter, Thermal Sensor와 같은 코어의 직접연관된 인터럽트를 수행하는 역활을 한다. LAPIC은 HPET를 지원한다. HPET란 높은 정밀도의 타이머로써, 각각의 코어들이 하나의 타이머에 대해서 경쟁하지 않아도 현재 타임에 대한 정확한 값을 가져올 수 있도록 도와준다. 만약 APIC이 활성화되어 HPET가 지원되면 8253pic은 사용되지 않도록 비활성화 된다.

각각의 인터럽트들이 어떻게 행동할지에 대한 정의는 Local vector table (LVT)라는 것을 통해서 설정할 수 있다. LVT는 APIC, xAPIC과 같은 경우에는 MMIO를 통해서 메모리 접근으로 컨트롤 하였으며, x2APIC과 같은 경우에는 MSR레지스터를 통해서 컨트롤 한다. Local Vector Table은 어떤 하드웨어 인터럽트를 코어의 인터럽트 핀으로 전달할지를 결정한다.

I/OAPCI

I/O APIC과 같은 경우는 외부 장비의 인터럽트를 적절한 코어에 전달하는 것이다. I/O APIC을 통해서 전달된 인터럽트는 LVT를 참고하여서 Local APIC으로 전달되어 최종적으로 코어에 전달된다. I/O APIC과 같은 경우에는 시스템 버스에 연결된 하드웨어나 I/O Device로부터 생성된 인터럽트를 코어에 전달하는 것이다.

I/O APCI은 Redirection table을 가지고 있다. 이는 각각의 장치에서 들어온 인터럽트를 지정된 인터럽트 번호로 매핑시킨다. 기존의 8253인터럽트 침과 같은 경우는 오직 16개의 외부 인터럽트만을 지원하였는데, APIC은 redirection을 통해서 하드웨어에 할당된 0x20이전의 인터럽트를 제외한 최대 224개의 인터럽트를 추가로 지원할 수 있다.

APIC Timer

APIC은 3개의 타이머 모드를 허용한다.

- Periodic Mode

- Periodic Mode에서는 소프트웨어가 (Typically, 운영체제가 된다.) 특정한 기간을 설정하여서 APIC에게 주기적인 Timer interrupt을 발생 시켜 달라고 요청하는 모드이다. 예를 들어서 Perioidic 모드에서는 소프트웨어는 APIC에 1ms마다 주기적으로 타이머 인터럽트를 넣어달라고 요청하게 된다.

- One-shot Mode

- Periodic Mode와 비슷하지만, 단 한번만 일어나도록 요청을 내리는 모드이다. 소프트웨어는 APIC에거 얼마간 뒤에 타이머 인터럽트를 발생 시켜 달라고 요청하게 된다. 예를 들어서 소프트웨어는 APIC에게 1ms뒤에 타이머 인터럽트를 넣어달라고 요청하게 된다.

- TSC-Deadline Mode

- TSC Deadline Mode는 다른 두개의 타이머 모드와는 약간 이질적인 특성이 있다. 특정 Timer interval을 전송하는 것이 아니라, TSC라는 코어의 Time stamp counter의 값이 특정 값 이상이 되면 타이머 인터럽트를 넣어달라고 요청하는 방법이다. 이 방식은 다른 두개의 방식보다 더욱 정확한 TSC라는 Timer을 사용하고 (다른 방식들은 CPU Frequency를 사용한다), Race condition을 피하기 쉬운 특징이 있다. 예를 들어서 소프트웨어는 APIC에게 현재 TSC Count가 100000 일경우 100000 + [math]\displaystyle{ \alpha }[/math]인 100050이 되면 타이머 인터럽트를 발생시켜 달라고 요청하게 된다.

References

- Intel 64 and Ia-32 Software Developer's Manual