개요

가상머신에서 돌리는 운영체제는 그 자체의 메모리 요구를 하게 된다. 예를 들어서 가상머신의 가상 프로세스가 프로세서에게 특정 Virtual Address를 통하여 어떤 위치에 있는 정보를 읽어오고 싶다고 하면, 가상머신은 그 명령을 가로채서 적절한 호스트 운영체제의 가상 주소로 변환하여야 한다. 즉 가상머신은 가상의 MMU를 에물레이트 하여야 하는 것이다 (Shadow Paging). 하지만 이러한 가상 머신의 메모리 주소 변환에 따른 메모리 접근의 가상화는 모든 가상머신의 OS 커널이 요구하는 모든 가상 주소 변환에 대한 요청에 대해서 처리되어야 하기 때문에 (CR3 레지스터 접근, Exception, MMU를 통한 VA-PA 변환) 호스트 운영체제에 큰 부담을 주게 된다. 이러한 요구를 하드웨어적으로 지원하기 위한 방식이 바로 Intel의 EPT이다.

구조

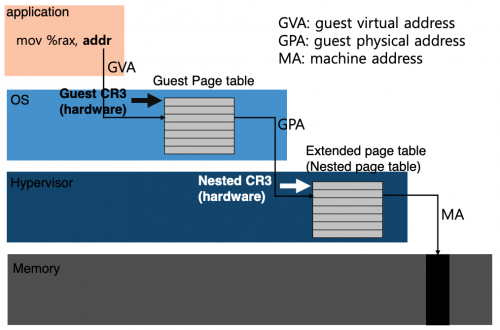

비가상화 환경에서 물리 주소와 가상 주소의 변환이 MMU를 통하여 두단계의 주소 체계를 가진다면, 가상화 환경에서는

- 가상 주소 -> 가상 물리 주소 -> 물리 주소

의 변환을 거쳐야 한다. 가상 머신에서 동작하는 게스트 운영체제는 가상화 환경에서 동작한다는 사실을 모른다. 따라서 가상 머신은 가상화되지 않은 환경에서 동작할 때와 마찬가지로 가상 주소와 물리 주소를 그대로 사용한다. 하지만 가상 머신이 아는 물리 주소는 실제 주소가 아니기 때문에 하이퍼바이저는 이를 실제 물리 주소로 변환하여야 한다. 이를 Shadow paging이라고 한다.

이러한 가상 주소를 머신 주소를 바꾸는 기능의 오버헤드를 줄이기 위해서 AMD와 인털에서 개발한 기술이다. AMD는 중첩 페이지 테이블로 부르기도 하는데 하는 일은 거이 EPT와 같다. 중첩 페이지 테이블은 CPU가 내보내는 가상 주소를 게스트 운영체제가 구축한 페이지 테이블을 통해서 물리 주소로 변경하고, 변경한 물리 주소를 다시 하이퍼바이저가 구축한 중첩 페이지 테이블을 통해서 머신 주소로 변경하여 메모리에 접근한다. 이를 위하여 가상 머신의 논리 주소와 머신 주소를 연관하는 주소를 소프트웨어 적으로가 아닌 하드웨어 적으로 한번에 변환시켜주는 것을 일컷는다. CPU가 게스트 모드에 있으면 주소를 게스트 모드 주소에서 머신 주소로 변환하고 CPU가 호스트 모드면 주소를 호스트 모드 주소에서 머신 주소로 변환한다. 추가적으로 프로세서는 Nested TLB라는 캐시를 유지하여 게스트의 물리 주소를 시스템의 물리 주소로 변환하는 캐시를 유지하여 위와 같은 작업이 빠르게 일어날 수 있도록 하였다.

오버헤드

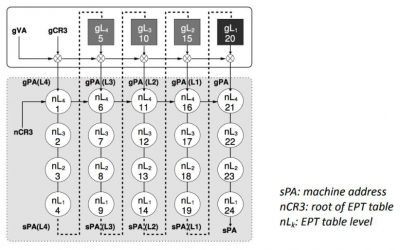

EPT워킹을 위해서는 각 Guest page table의 Physical address에 접근할 때 마다 Extended page table워킹이 발생한다. 즉 4 + 4 * 4 = 20번의 page table워크가 발생한다. 근데, CR3접근또한 EPT walk가 발생함으로, 4번의 워크가 필요하다. 여기다가 데이터 접근 또한 필요함으로 총 4 + 4 * 4 + 4 + 1 = 25번의 메모리 접근이 필요하게 된다. 이러한 오버헤드를 줄이기 위해서 인텔은 EPT도 (즉 GPA->HPA 변환을) TLB처럼 캐싱해서 EPT워크의 필요성을 줄이기 위해서 노력하였다. 그러나 만약 캐쉬가 없다면 25번의 Walk가 필요해지기 때문에, EPT를 쓰더라도 Native에 비해서 성능 하락이 오는 것을 피할 수는 없다.